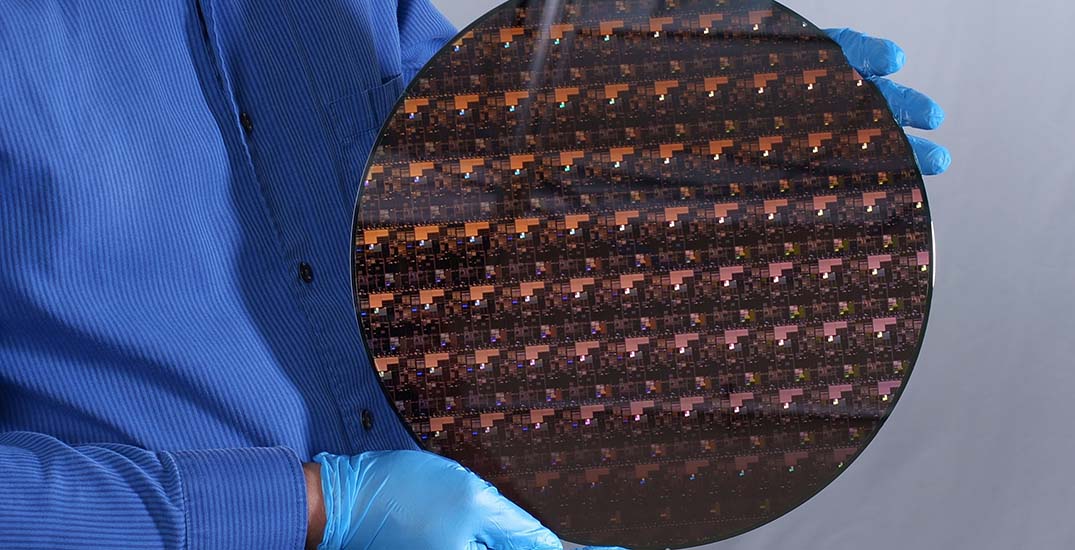

IBM has claimed a breakthrough in semiconductor design and process with the development of the world’s first chip announced with 2-nanometer (nm) nanosheet technology.

With demand for increased chip performance and energy efficiency rising – especially in the era of hybrid cloud, AI, and the Internet of Things – IBM’s new 2 nm chip technology helps is projected to achieve 45% higher performance, or 75% lower energy use, than today’s most advanced 7nm node chips.

The potential benefits of 2nm chips could include:

* Quadrupling cell phone battery life, only requiring users to charge their devices every four days.

* Slashing the carbon footprint of data centers, which account for 1% of global energy use. Changing all of their servers to 2 nm-based processors could potentially reduce that number significantly.

* Drastically speeding up a laptop’s functions, ranging from quicker processing in applications, to assisting in language translation more easily, to faster internet access.

* Contributing to faster object detection and reaction time in autonomous vehicles like self-driving cars.

“The IBM innovation reflected in this new 2nm chip is essential to the entire semiconductor and IT industry,” says Darío Gil, senior vice-president and director of IBM Research. “It is the product of IBM’s approach of taking on hard tech challenges and a demonstration of how breakthroughs can result from sustained investments and a collaborative R&D ecosystem approach.”

IBM’s legacy of semiconductor wins includes the first implementation of 7nm and 5nm process technologies, single cell DRAM, the Dennard Scaling Laws, chemically amplified photoresists, copper interconnect wiring, silicon on insulator technology, multi core microprocessors, high-k gate dielectrics, embedded DRAM, and 3D chip stacking.

IBM’s first commercialised offering including IBM Research 7 nm advancements will debut later this year in IBM Power10-based IBM Power Systems.

Increasing the number of transistors per chip can make them smaller, faster, more reliable, and more efficient. The 2nm design demonstrates the advanced scaling of semiconductors using IBM’s nanosheet technology. It will allow the 2 nm chip to fit up to 50-billion transistors on a chip the size of a fingernail.

More transistors on a chip also means processor designers have more options to infuse core-level innovations to improve capabilities for leading edge workloads like AI and cloud computing, as well as new pathways for hardware-enforced security and encryption.